## 5.2 FED(Field Emission Display)의 개발사

| [丑 5-2] [ | EDS | 개 | 발사 |

|-----------|-----|---|----|

|-----------|-----|---|----|

| 연도        | 개 발 내 용                                               |  |  |  |

|-----------|-------------------------------------------------------|--|--|--|

| 1897년     | - Wood가 고전계하에서 전계방출 실험.                               |  |  |  |

| 1926년     | - 양자역학적 tunneling으로 전계방출 이론 정립.                       |  |  |  |

| 1928년     | - Fowler와 Nordheim이 전계방출 현상을 이론식으로 표현.                |  |  |  |

| 1958년     | - Buck와 Shoulders가 1 µm scale 첫 제안.                   |  |  |  |

| 1959년     | - Feyman이 분자 수준의 미세 구조로 접근.                           |  |  |  |

| 1961년     | - Shoulders가 진공 미세소자인 microtriodes 제안.                |  |  |  |

| 1968년     | - SRI사의 Spindt가 Spindt혱 cathode array 제작.             |  |  |  |

| 1979년 - 8 | - Brodie와 Spindt가 100-tip cathode array 제작.           |  |  |  |

|           | - Brodie와 Spindt가 microwave 소자 개발.                    |  |  |  |

| 1985년     | - Meyer 등이 최초의 monochrome display 개발.                 |  |  |  |

| 1986년     | - Lally 등이 최초의 microwave tube 개발.                     |  |  |  |

| 1987년     | - Holland 등이 첫 high resolution display(300 color) 개발. |  |  |  |

| 1993년     | - LETI사가 6° full color FED 개발.                        |  |  |  |

| 1994년     | - Micro Display Tech.사가 0.7" Si emitter color FED 개발  |  |  |  |

| 1996년     | - Samsung사가 4° color FED 개발.                          |  |  |  |

| 1997년     | - Motorola사가 5° color FED 개발.                         |  |  |  |

| 2001년     | - Samsung사가 7° CNT-FED 개발.                            |  |  |  |

| 2002년     | - LG전자가 20° FED 개발                                    |  |  |  |

| 2003년     | - Samsung SDI가 30° CNT-FED 개발                         |  |  |  |

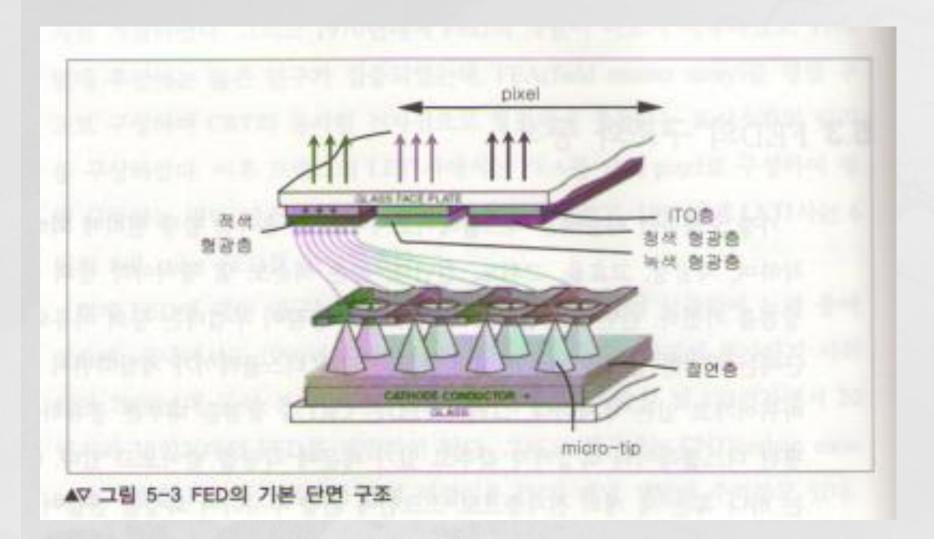

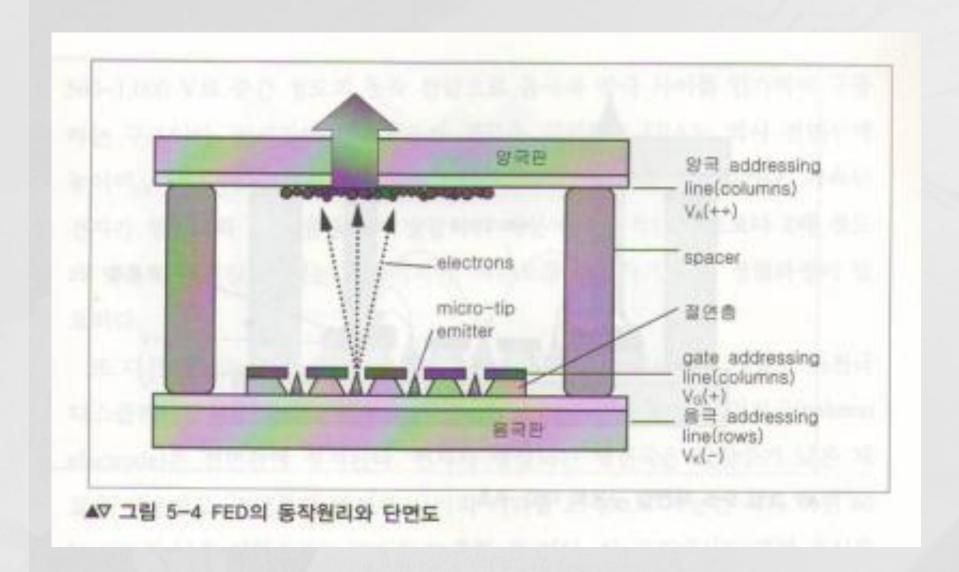

# 5.3.1 FED의 구조와 동작

### FED의 동작원리와 단면도

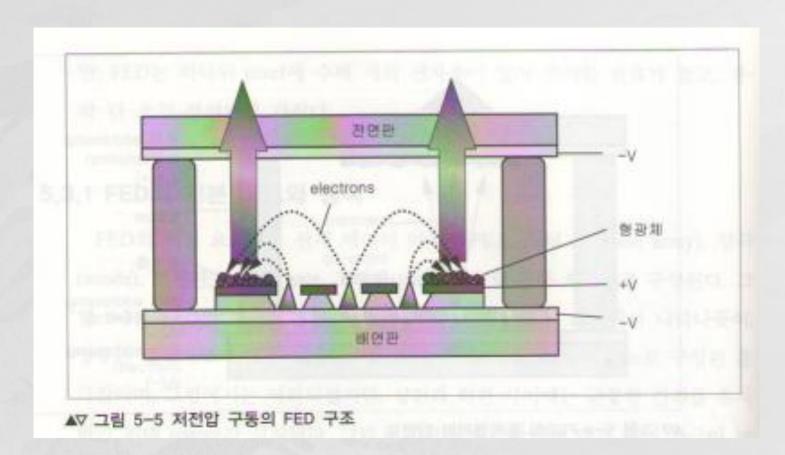

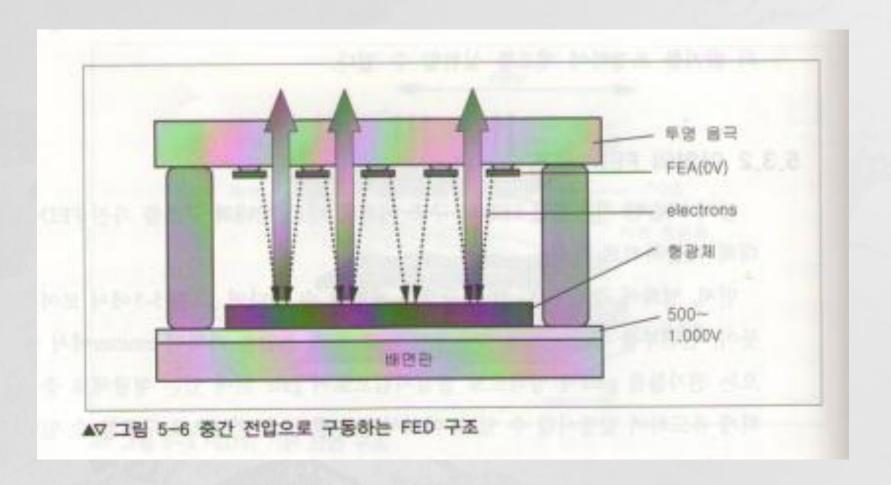

## 5.3.2 이외의 FED 구조

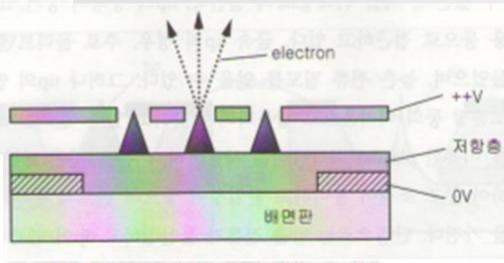

o 저전압 구동의 FED 구조

• 중간 전압 구동의 FED 구조

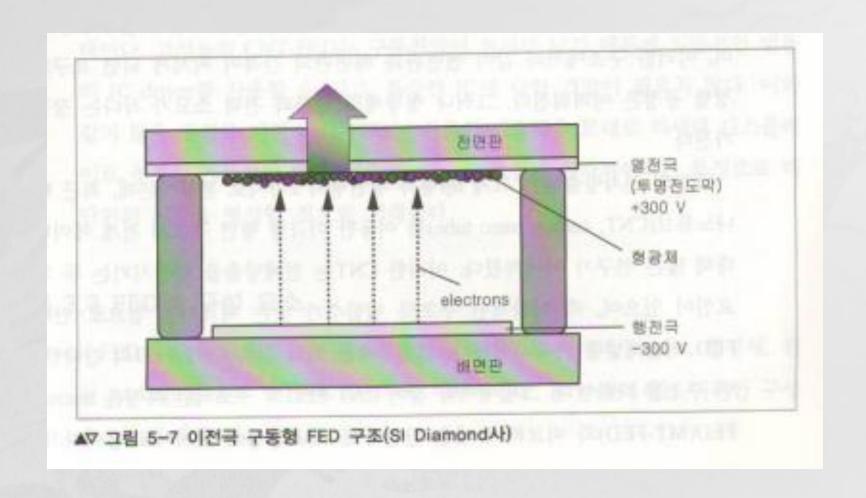

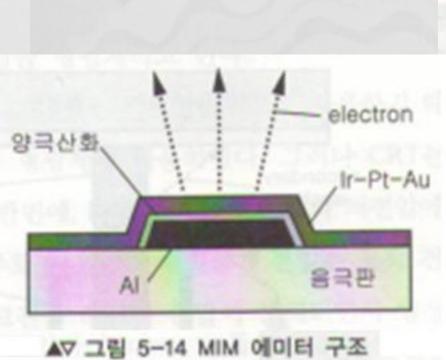

#### o 이전극구동형 FED 구조(SI Diamond사 제작)

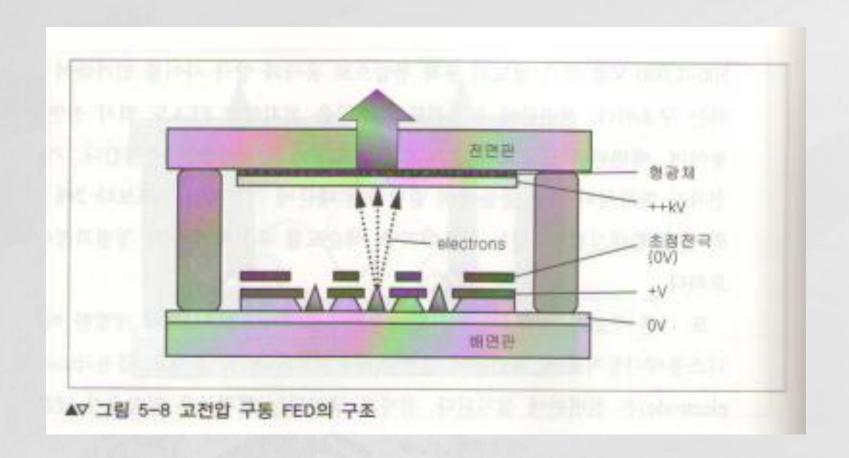

#### • 고전압 구동의 FED 구조

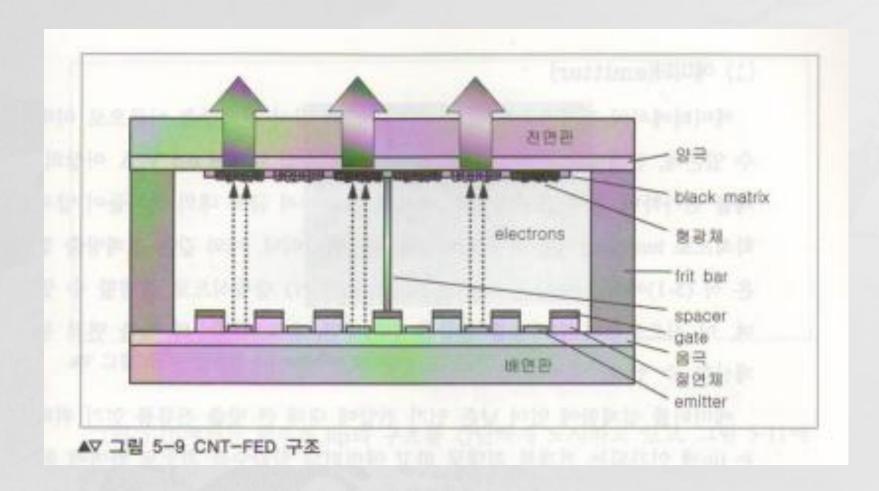

#### • CNT-FED 구조

### 5.3.3 FED의 구성 요소

• FED의 핵심 요소 기술은 전자방출원을 중심으로 에미터, spacer, 형광체, 진공 packaging 공정 및 구동 회로부.

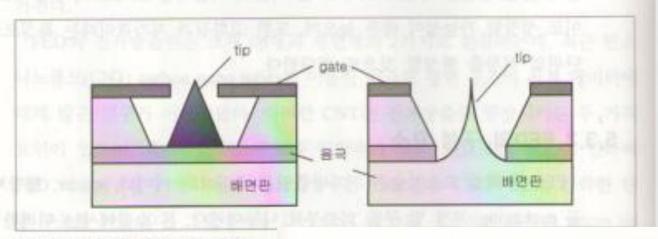

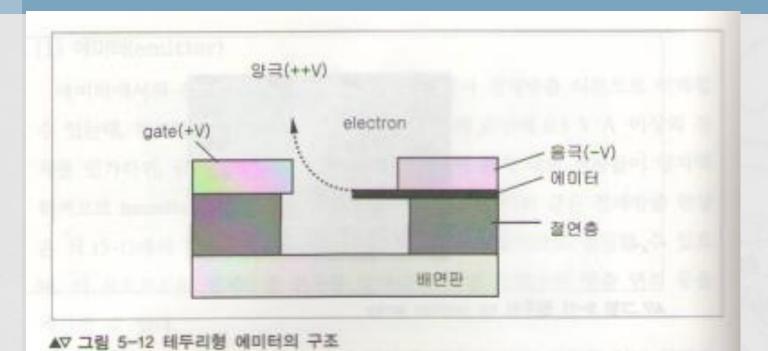

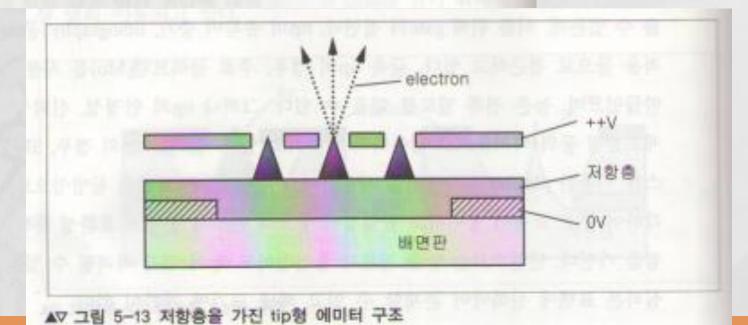

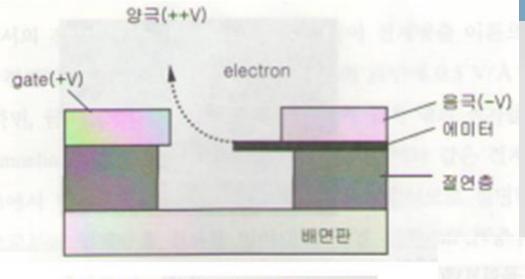

(1) 에미터(emitter)

▲▽ 그림 5-10 원추형 tip의 구조

▲▽ 그림 5-11 원추형 tip emitter array

▲▽ 그림 5-12 테두리형 에미터의 구조

▲▽ 그림 5-13 저항층을 가진 tip형 에미터 구조

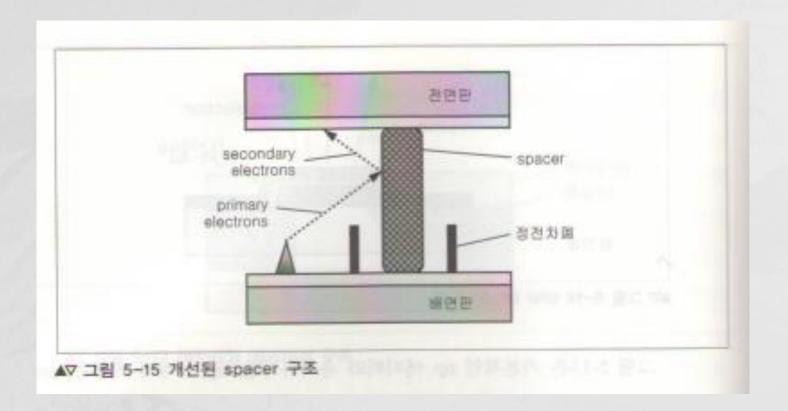

#### (2) Spacer

### (3) 형광체

[표 5-3] 형광체 물질의 종류와 효율

| 재료                                  | 克音  | 색 삼        | 전 알[V] |

|-------------------------------------|-----|------------|--------|

| ZnO                                 | 16  | 청색/녹색      | 32     |

| SnO <sub>2</sub> :Eu                | 2.0 | 적색         | 10     |

| ZnGa <sub>2</sub> O <sub>4</sub>    | 0.7 | 청색         | 30     |

| La <sub>2</sub> O <sub>2</sub> S:Tb | 5.2 | 녹색         | 300    |

| Y <sub>2</sub> O <sub>2</sub> S:Eu  | 2.2 | 정색         | 300    |

| LaOBr:Tb                            | 0.5 | 청색         | 300    |

| Gd <sub>2</sub> O <sub>2</sub> S:Tb | 7.9 | 녹색         | 500    |

| ZnS:Ag                              | 0.8 | <b>참</b> 색 | 500    |

| Y <sub>2</sub> O <sub>5</sub> :Eu   | 9   | 적색         | 5,000  |

| ZnS:Ag. Al                          | 4   | 청색         | 5,000  |

## 5.4 FED 소자의 제조공정

- 원추형 tip 에미터의 제조공정

- o 에미터의 소재로는 주로 금속과 실리콘으로 형성되는 tip의 공정

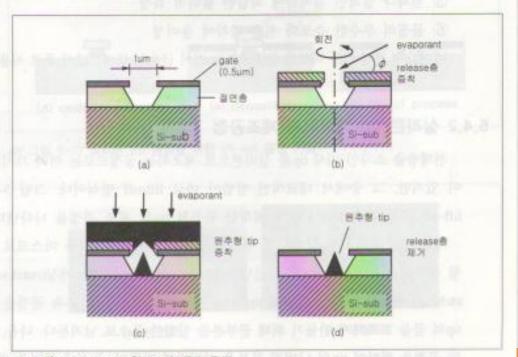

### 5.4.1 금속 tip 에미터의 제조공정

- 원추형 tip 에미터의 제조공정은 박막공정을 기초로 만들어짐.

- 그림 5-16은 Spindt형 tip의 제조공정을 보여줌

- (a) 유리 혹은 실리콘 기판위에 음극용 금속박막을 증착함. 절연층과 gate금속을 그위에 증착함.감광막(photoresist)을 스핀코팅을 이용하여 1µm 정도 증착함. 사진식각공정을 통하여 홀 패턴을 만듦

- (b) 분리층을 형성함.

- (c) 원추형 tip을 구성하기위해 기판에 수 직방향으로 몰리브덴(Mo)을 증착시킴.

- (d) 분리층을 제거하면 위에 덮인 Mo층까지 제거되어 금속 tip이 형성됨.

### 원추형 에미터로 사용가능한 금속의 특성

- ① 용융점이 충분히 높고, 낮은 증기압을 가짐.

- ② 낮은 일함수

- ③ 기판과의 우수한 접착력

- ④ 분리층 식각 시에 잘 견딤.

- ⑤ 전계나 열적인 첨예화에 적합한 물리적 특성.

- ⑥ 물질의 우수한 순도와 진공 증착에 용이성이 우수함.

### 5.4.2 실리콘 tip 에미터의 제조공정

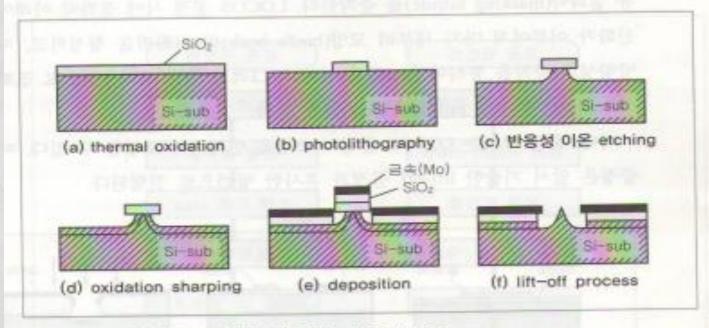

- 실리콘 tip 에미터의 제조공정중 대표적인 방식이 lift-off 방식임.

- 그림 5-17은 lift-off 공정을 이용한 tip의 제조공정을 보여줌

- (a) 실리콘 기판위에 산화막을 형성하고 패턴닝을 함.

- (b) Photolithography 공정.

- (c) 반응성 이온을 이용한 etching 과정.

- (d) Oxidation sharping 과정.

- (e) 분리를 위한 deposition 과정

- (f) Lift-off 과정을 통한 실리콘 tip이 형성됨.

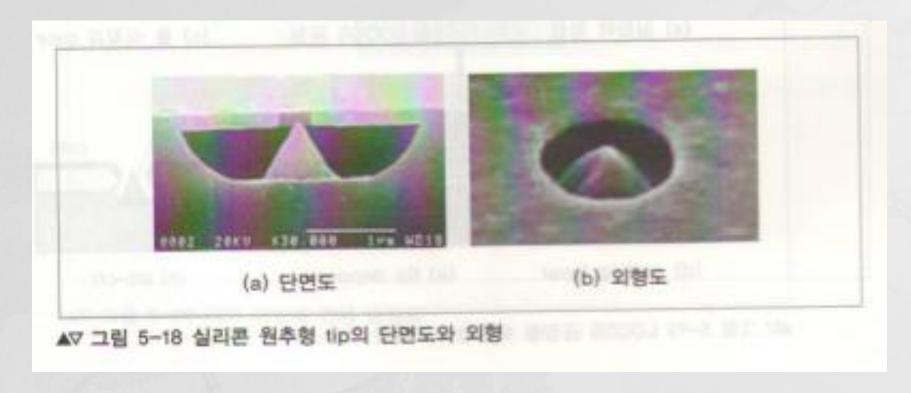

#### 실리콘 원추형 tip의 단면도와 외형

LOCOS 공정을 이용한 원추형 tip의 제조과정 그림 5-19(p. 230)

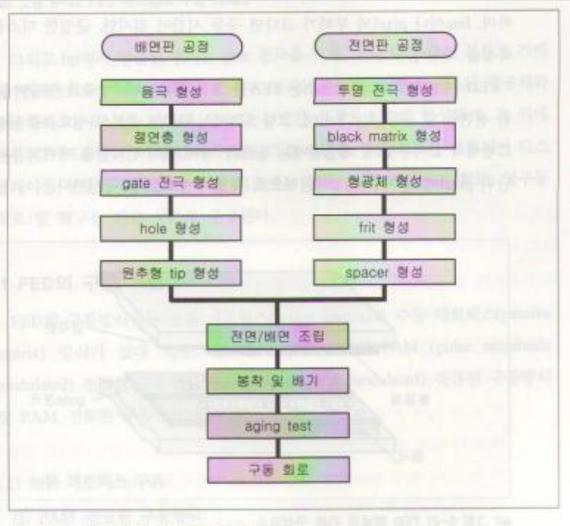

#### 5.4.3 FEA 패널의 제조공정

• 그림 5-20은 FEA를 포함한 배면판과 형광체를 포함한 전면판을 합 착하여 FED Panel을 만드는 전체공정도를 나타낸 것임.

▲▽ 그림 5-20 FED 패널의 전체 공정도