IT CookBook, 최신 VLSI 설계, 조준동, 성균관대학교

- ➤ MOSFET의 동작과 특성을 알아본다.

- ▶ CMOS의 구조와 동작 원리를 이해한다.

- ▶NMOS의 세 가지 동작상태에 대해서 알아본다.

- ▶NMOS 채널 전류 공식을 이해한다.

## 1.CMOS의 구조 및 동작 원리

2.NMOS의 동작과 특성

#### <u>1.1 CMOS의 출현 배경</u>

- 실리콘 게이트 NMOS 기술은 1970년대와 1980년대 초반기의 주류 기술로서 반도체 기술의 발전을 주도하였다.

- 1990년대에 들어서 한 칩에 집적되는 트랜지스터의 개수가 백만 개를 넘어서자 NMOS 기술의 한계가 나타나기 시작한다.

- NMOS 기술은 논리회로를 구현하는 데 필요한 소자의 개수가 적은 대신 전력을 많이 사용하였는데, 전력소모에 따른 과열이 큰 문제로 등장하였다.

- 전력소모를 줄이기 위해 NMOS와 PMOS를 상보적으로 사용하는 CMOS 기술이 사용되기 시작하였으며, 현재 반도체 집적회로의 핵심 기술로 자리잡고 있다.

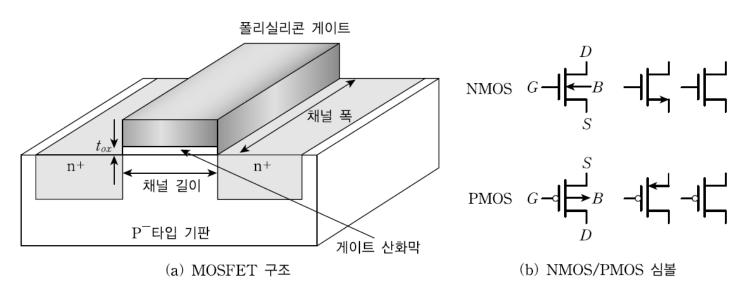

#### <u>1.2 MOSFET 구조</u>

[그림 4-2] MOSFET(NMOS)의 구조와 NMOS/PMOS의 심볼

- P-타입의 실리콘 기판 위에 이산화 규소(SiO<sub>2</sub>)로 이루어진 산화막이 존재하고,

그 위에 도체의 역할을 하도록 도핑을 많이 하여 전도도를 높인 폴리실리콘 게이트가 위치하는 구조

- MOS 구조로 이루어진 중앙부의 게이트 아래 부분을 채널 영역(반전층)이라고 하는데, 이 부분은 게이트 전압에 따라 소스와 드레인을 전기적으로 연결하는 핵심적인 역할을 한다.

#### <u>1.3 NMOS와 PMOS의 구조 및 동작 원리</u>

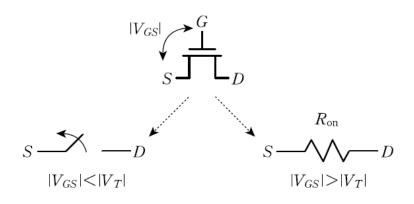

[그림 4-3] NMOS의 스위치 모델

- 인버전 : 소스와 게이트 사이의 전압  $V_{GS}$ 가 문턱전압보다 높은 전압이 걸리면 게이트 아래 쪽 실리콘 기판에 충분한 양의 전자가 유기되어 채널을 형성한다.

- 컨덕션 : 드레인에 소스보다 높은 전압을 걸어주면 형성된 채널(반전층)을 통해 전자가 이동하여 전류가 흐른다.

#### <u>1.3 NMOS와 PMOS의 구조 및 동작 원리</u>

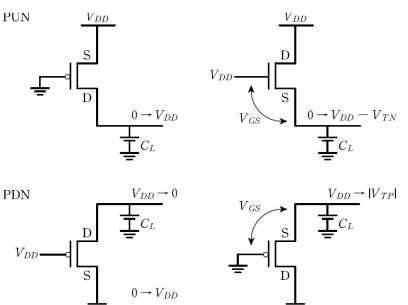

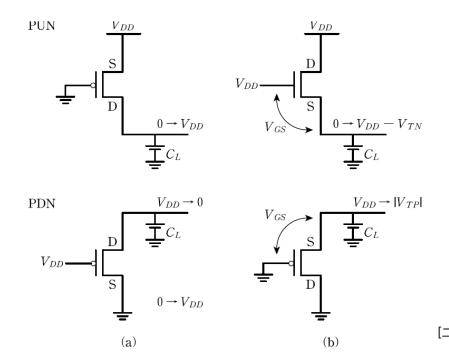

- [그림 4-4(a)]처럼 풀 업 네트워크인 PMOS의 소스가 공급전압  $V_{DD}$ 에 연결되고 풀 다운 네트워크인 NMOS의 소스가 GND에 연결된 경우에는 출력이  $V_{DD}$  또는 0의 출력 스윙 결과를 보인다.

- [그림 4-4(b)]처럼 NMOS의 드레인이  $V_{DD}$ 에 연결되고, PMOS의 드레인이 GND에 연결된 경우에는  $V_{DD}$ - $|V_{TN}|$ ,  $|V_{TP}|$ 와 같이 출력 스윙이 문턱전압만큼의 차이를 보인다.

(b)

(a)

[그림 4-4] NMOS 및 PMOS의 문턱전압 손실

#### <u>1.3 NMOS와 PMOS의 구조 및 동작 원리</u>

- CMOS 인버터는  $V_{DD}$  또는 0의 완전 스윙의 출력을 제공하기 위하여 [그림 4-4(a)]와 같은 구조를 사용

- [그림 4-4(b)]: NMOS나 PMOS를 하나만 쓰는 스위치에서 볼 수 있는 형태로, 문턱전압의 손실로 인해 팬아웃 게이트에서 정전전력이 소모되어 사용하지 않는다.

#### <u>1.3 NMOS와 PMOS의 구조 및 동작 원리</u>

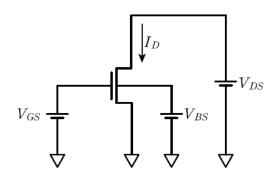

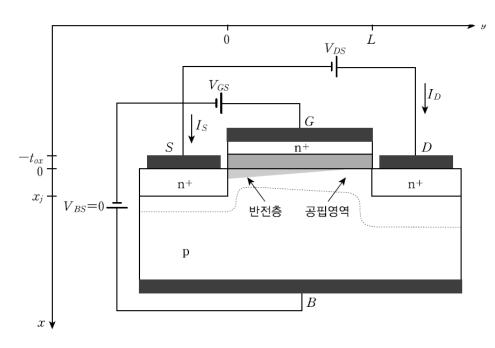

- MOS는 소스, 게이트, 드레인, 백 게이트(혹은 벌크)의 네 단자로 구성

- MOS는 전압을 인가하여 2단자를 비교할 때,

n형이면 고전압 쪽이 드레인, 저전압 쪽이 소스가 되고

p형이면 그 역이 된다.

- 즉 소스, 드레인의 명칭은 캐리어의 도통 방향에 의해 결정

- [그림 4-5]는 드레인과 소스 사이의 전류( $I_D$ ), 드레인-소스 전압( $V_{DS}$ ), 벌크-소스 전압( $V_{BS}$ ), 게이트-소스 전압( $V_{GS}$ ), 문턱전압( $V_T$ )을 정의하고 있다.

[그림 4-5] NMOS의 전압 및 전류

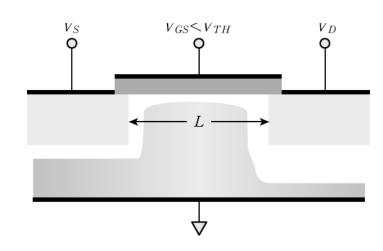

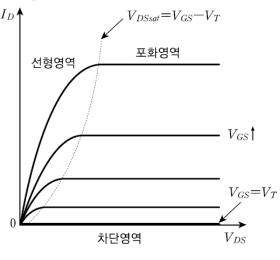

#### 2.1 NMOS의 세 가지 동작 상태

#### □ 차단상태

[그림 4-6] NMOS의 차단 상태

- 게이트-소스 전압과 게이트-드레인 전압이 문턱전압보다 낮으며(즉,  $V_{GS} < V_{T}$ ,  $V_{GD} < V_{T}$ ), 드레인-소스 전압  $V_{DS}$ 가 0보다 큰 경우.

- => 게이트가 닫혀 드레인과 소스 사이에 전류가 흐르지 못한다(즉,  $I_D=0$ ).

- 실제로는 소스에 있는 전자 중에서 에너지가 높은 일부 전자들이 채널로 들어가서 드레인으로 흐르는 것이 가능한데, 이것이 문턱아래 전류가 된다.

- 트랜지스터가 차단 스위치로 사용될 때 이상적으로는 드레인과 소스 사이의 전류가 없어야 하지만, 실제로는 미약한 역전류가 흐르고 있는데 이를 문턱아래 누설전류라고 부른다.

#### 2.1 NMOS의 세 가지 동작 상태

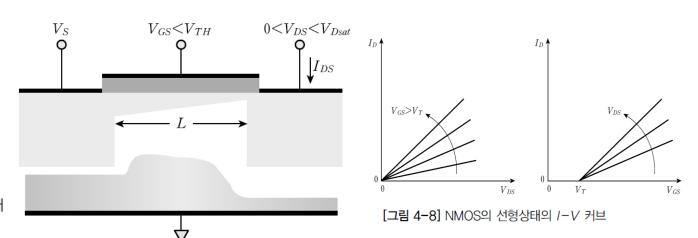

#### □ 선형상태

- $V_{GS}$ 와  $V_{GD}$ 가 문턱전압  $V_T$ 보다 크고(즉,  $V_{GS}>V_T$ ,  $V_{GD}>V_T$ ),  $V_{DS}$ 가 0보다 크고 포화상태 전압보다 작은(즉,  $V_{Dsat}>V_{DS}>0$ ) 경우

- 선형상태에서는 게이트가 열려서 채널이 형성되며 소스에서 드레인 방향으로 전류가 흐른다.

- 선형상태에서 게이트에 정전압이 인가되면 소스-드레인 사이 채널에 전자가 유도되어 반전층이 만들어진다. 이 상태에서는  $V_{DS}$ 가 비교적 낮고  $V_{GD}$ 가 문턱전압  $V_{T}$ 를 넘게 되며, 소스-드레인 사이의 반전층이 저항 같은 기능을 가지게 된다.

[그림 4-7] NMOS의 선형상태

#### 2.1 NMOS의 세 가지 동작 상태

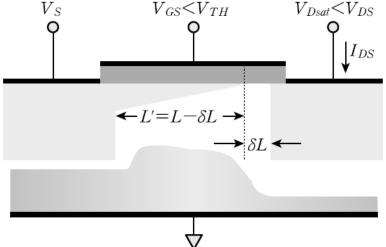

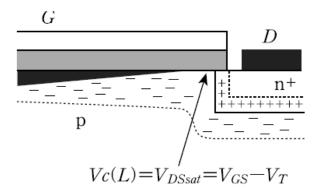

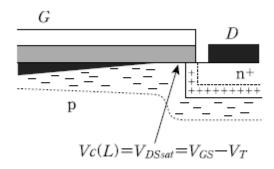

#### □ 포화상태

- 게이트-소스 전압이 문턱전압보다 크고 게이트-드레인 전압이 문턱전압보다 작으며 드레인-소스 전압이  $V_{Dsat}$ 보다 큰 경우(즉,  $V_{GS}>V_T$ ,  $V_{GD}<=V_T$ ,  $V_{DS}>=V_{Dsat}$ )

- 포화상태에서는 게이트가 열리고 채널이 형성되어 소스와 드레인 사이에 전류  $I_D$ 가  $V_{DS}$ 의 증감에 관계없이 일정하게 흐른다(즉,  $I_D$ = $I_{Dsat}$ ).

• 포화상태에서  $V_{GD}$ 가 문턱전압  $V_{T}$ 보다 밑돌게 되면 드레인 영역 부근에서 반전층이 형성되지 않는다.

#### 2.1 NMOS의 세 가지 동작 상태

#### □ 포화상태

- 여기서  $V_{GD}=V_T$ 의 상태를 핀치오프라고 부른다.

- 핀치오프 상태를 포화영역이라고 부름. MOS 컨덕턴스는 반전층의 길이에 의해서 일정해진다.

- 포화영역에서는 드레인 전압이 게이트 전압보다 높아서 채널 중의 일부분이 없어짐

- 채널 길이 L이 줄어들면  $I_{DS}$ 가 증가하고,  $V_{DS}$ 가 증가하면  $\delta$ L(게이트 길이의 변화)이 커진다.  $V_{DS} = V_{GS} V_{TH}$ 가 되면 수직 전기장이 줄어들어 채널이 좁아지게 되고 전자는 공핍영역으로 진행된다.

#### 2.2 NMOS 채널 전류 공식

[그림 4-11] NMOS의 단면도와 전류 공식에 사용되는 기하학적 표기

• µn: 전하 운반자의 유효 이동도

• L: 게이트길이

$$I_{y} = W Q_{n}(y) V_{y}(y) \tag{4.1}$$

$$I_D = -WQ_n(y)V_{\nu}(y) \tag{4.2}$$

$$v_y(y) \simeq -\mu_n E_y(y) = \mu_n \frac{dV_c(y)}{dy}$$

(4.3)

• W : 게이트 폭

•  $C_{ox}$ 는 단위면적당 게이트 산화층의 정전용량

#### □ 선형영역

$$Q_n(y) = -C_{ox}(V_{GS} - V_C(y) - V_T) \tag{4.4}$$

$$I_D = W \mu_n C_{ox} (V_{GS} - V_C(y) - V_T) (dV_C(y) / dy)$$

(4.5)

$$I_D dy = W \mu_n C_{ox} (V_{GS} - V_C - V_T) dV_C \tag{4.6}$$

$$I_D \int_0^L dy = W \mu_n C_{ox} \int_0^{V_{DS}} (V_{GS} - V_C - V_T) dV_C$$

(4.7)

$$I_D = W/L \,\mu_n C_{ox} (V_{GS} - V_{DS}/2 - V_T) V_{DS} \tag{4.8}$$

$$I_D = W/L \,\mu_n C_{ox} (V_{GS} - V_T) V_{DS} \tag{4.9}$$

#### □ 선형영역

$$I_D = W/L \,\mu_n C_{ox} (V_{GS} - V_T) V_{DS} \tag{4.9}$$

- 식 (4.9)에서 V<sub>DS</sub>, V<sub>GS</sub>, W, L의 증가에 따른 I<sub>D</sub>의 변화

- $V_{DS}$ 가 증가하면 높은 수평 전기장의 영향으로  $I_{D}$ 가 증가한다.

- $V_{GS}$ 가 증가하면 높은 전자 집중의 영향으로  $I_D$ 가 증가한다.

- L이 증가하면 낮은 수평 전기장의 영향으로 I<sub>D</sub>가 감소한다.

- W가 증가하면 넓은 전도 채널의 영향으로 I<sub>D</sub>가 증가한다.

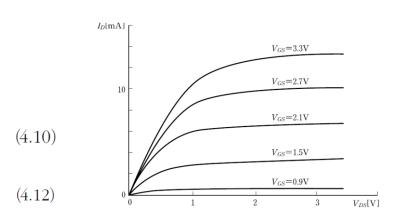

#### □ 포화영역

[그림 4-12] 전류 포화 현상

$$I_D = W/2L \, \mu_n C_{ox} (V_{GS} - V_T)^2$$

$$I_{Dsat} = W/2L \, \mu_n C_{ox} (V_{GS} - V_T)^2 \left[ 1 + \lambda (V_{DS} - V_{DSsat}) \right]$$

[그림 4-13] 핀치오프 포인트(소스에서  $V_{C} = 0$ )에서의 전압

[그림 4-14] MOS 트랜지스터의 측정된 전류 전압 특성(W/L=25/0.35』m)

• [그림 4-12]를 살펴보면  $V_{DS}$ 가 증가하며,  $V_{DSsat} = V_{GS} - V_{T}$ 에 접근할 때  $|E_{y}|$ 가 증가하고  $|Q_{h}|$ 이 감소한다. 이 경우에 전류 포화가 발생한다.

#### □ 포화영역

$$Q_n(L) = -C_{ox}(V_{GS} - V_{DS} - V_T) = 0 (4.11)$$

- 이러한 현상이 앞에서 설명한 핀치오프이며, 이 핀치오프 지점에서의 전압은  $V_C(L) = V_{DSsat} = V_{GS} V_T$ 가 된다.

- 반전층이 거의 사라져서 채널 길이가 아주 짧아지면, 전하 운반자의 이동은 유사-탄도성 전달을 하며, I-V 특성을 위의 식 (4.10)으로 근사시킬 수 없다.

[그림 4-13] 핀치오프 포인트(소스에서  $V_C = 0$ )에서의 전압

# Thank You

4장 MOSFET의 구조 및 특성 끝